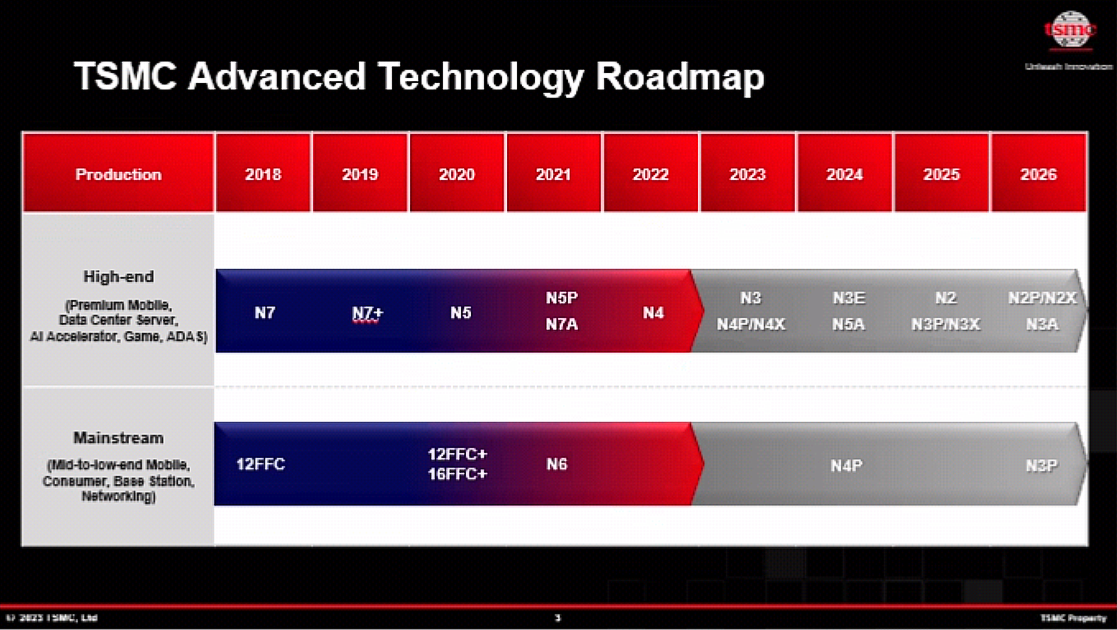

TSMC sẵn sàng N2P và N2X: 2nm với hiệu suất nâng cao

Tại Hội nghị chuyên đề về công nghệ Bắc Mỹ năm 2023, TSMC đã tiết lộ thêm thông tin về các công nghệ xử lý lớp 2nm sắp tới của họ sẽ sẵn sàng sản xuất vào năm 2025 – 2026. Xưởng đúc lớn nhất thế giới có kế hoạch mở rộng dòng sản phẩm N2 của mình với N2P sẽ có đường ray điện phía sau và hứa hẹn để tăng hiệu suất, giảm tiêu thụ điện năng và tăng mật độ bóng bán dẫn. Ngoài ra, TSMC lên kế hoạch cho N2X, một nút được thiết kế để mang lại hiệu suất tối đa và hỗ trợ điện áp cao hơn.

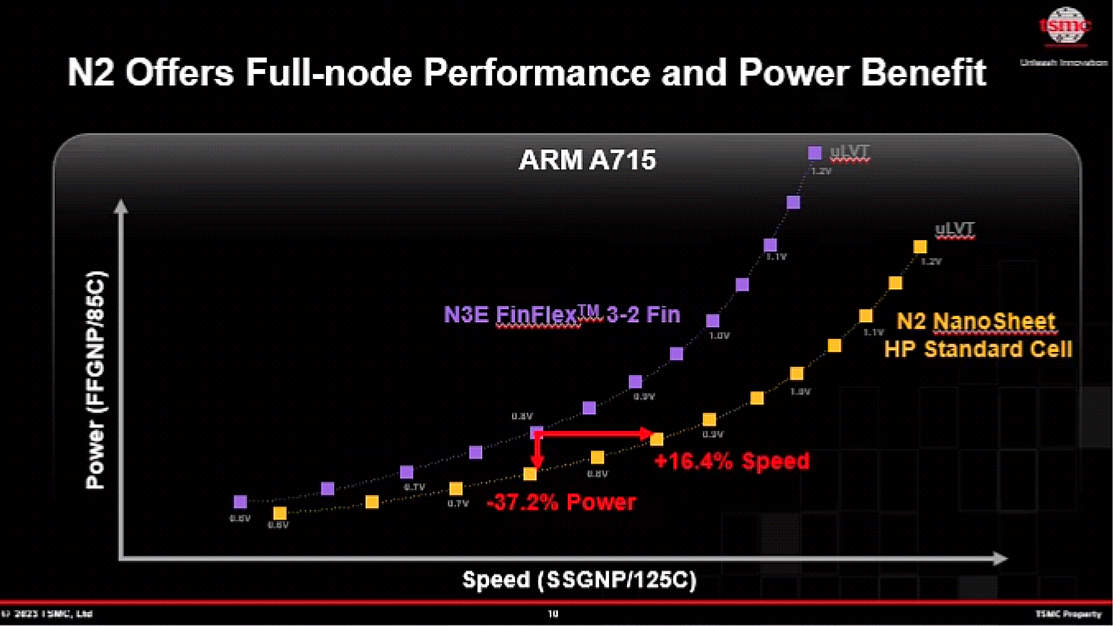

N2 cung cấp các ưu điểm của nút đầy đủ

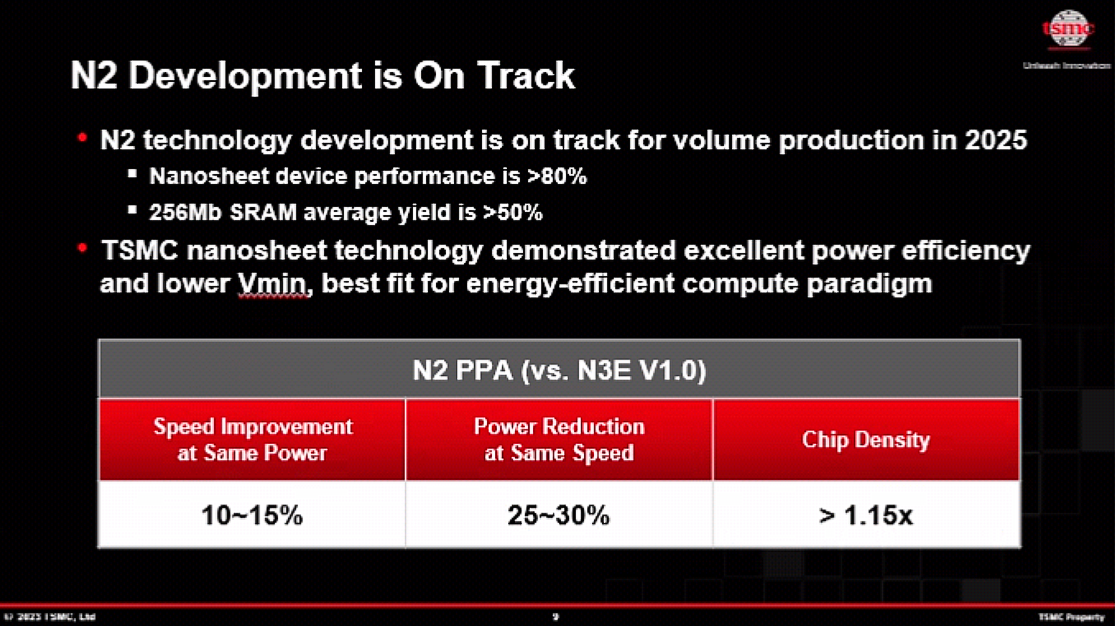

Công nghệ xử lý N2 ban đầu của TSMC, được thiết lập để đưa vào sản xuất số lượng lớn vào khoảng năm 2025, giới thiệu các bóng bán dẫn Nanosheet cổng tất cả xung quanh (GAA). Khi so sánh với N3E, nút mới hứa hẹn sẽ tăng hiệu suất từ 10% đến 15% với công suất và số lượng bóng bán dẫn giống hệt nhau hoặc giảm mức tiêu thụ điện năng từ 25% đến 30% trong khi vẫn duy trì cùng tần số và độ phức tạp. Khi nói đến việc mở rộng quy mô, TSMC không cung cấp các con số chi tiết, nhưng nói rằng công nghệ chế tạo mới sẽ cho phép tăng mật độ chip lên 15%, đây là một thuật ngữ mơ hồ vì nó phản ánh một IC giả định chứa 50% logic, 30% SRAM , và 20% mạch tương tự.

Tiến trình N2 của TSMC có vẻ như đã được lên kế hoạch. Tại hội nghị chuyên đề của mình, TSMC đã thông báo rằng hiệu suất bóng bán dẫn Nanosheet GAA của họ đã đạt hơn 80% thông số kỹ thuật mục tiêu và năng suất trung bình của IC thử nghiệm SRAM 256Mb vượt quá 50%.

N2P: Đường ray điện mặt sau cho hiệu quả hoạt động cao hơn

Trong khi N2 cung cấp những lợi thế hữu hình so với N3E, thì N2P kế nhiệm của nó hứa hẹn sẽ còn ấn tượng hơn nữa. Quy trình lớp 2nm thế hệ thứ hai của TSMC được thiết lập để kết hợp mạng phân phối điện mặt sau (PDN) được thiết kế để tăng hiệu suất bóng bán dẫn, tiêu thụ điện năng thấp hơn, tăng mật độ bóng bán dẫn và loại bỏ rủi ro nhiễu giữa dữ liệu và dây nguồn trong chip.

Cung cấp năng lượng từ mặt sau là một trong những đổi mới quan trọng nhất trong những năm gần đây vì dòng sau (BEOL) và điện trở tiếp xúc đã từng là thách thức lớn của các nhà sản xuất chip trong một thời gian. Bằng cách di chuyển các đường ray nguồn ra phía sau tấm wafer, việc phân phối nguồn ở mặt sau sẽ tách I/O và hệ thống dây nguồn, đồng thời giảm thiểu mức tăng do các vấn đề về điện trở trong BEOL.

Mặc dù TSMC chưa cung cấp số liệu cụ thể về lợi ích về hiệu suất, công suất và diện tích (PPA) của N2P so với N2, nhưng một số nhà phân tích cho rằng PDN mặt sau có thể dẫn đến giảm mức tiêu thụ điện năng ở mức một con số và tăng mật độ bóng bán dẫn lên hai con số. Hãy nhớ rằng TSMC có thể sẽ tối ưu hóa hơn nữa cho N2P, hy vọng công nghệ này sẽ tiên tiến hơn đáng kể so với N2 và N3 cả về hiệu quả hoạt động và mật độ bóng bán dẫn.

TSMC hy vọng N2P sẽ sẵn sàng cho quá trình sản xuất số lượng lớn (HVM) vào năm 2026, vì vậy, mong đợi các chip thực tế được sản xuất trên nút này sẽ xuất xưởng vào năm 2027. Giả sử rằng Intel thực hiện lời hứa của mình và xuất xưởng những con chip đầu tiên được sản xuất trên công nghệ sản xuất 20A của mình (sử dụng cả hai RibbonFET GAA bóng bán dẫn và PDN mặt sau PowerVia) vào năm 2024, nó sẽ đi trước TSMC hai hoặc ba năm với đường ray điện mặt sau.

N2X: Điện áp cao cho hiệu suất cực cao

TSMC đang phát triển N2X, một quy trình chế tạo phù hợp với các ứng dụng điện toán hiệu năng cao (HPC), chẳng hạn như CPU trung tâm dữ liệu cao cấp. Nhìn chung, những con chip này ngốn điện và cần khả năng tăng xung nhịp khi có nhu cầu cao nhất. Điều này có nghĩa là chúng phải hỗ trợ điện áp và dòng điện cao. Do nút được thiết lập để ra mắt sớm nhất vào năm 2026, nên TSMC hiện không vạch ra những cải tiến về hiệu suất của nó so với N2, N2P và N3X. Trong khi đó, như với tất cả các công nghệ sản xuất gần đây, hiệu suất và hiệu quả tối đa chỉ có thể đạt được thông qua đồng tối ưu hóa công nghệ thiết kế mở rộng (DTCO) giữa xưởng đúc và nhà phát triển IP.