Cuộc đua sản xuất chip bán dẫn: Khoảng cách ngắn lại các công ty sản xuất

Năm 2009, ngành bán dẫn bắt đầu gặp khó khăn trong việc co lại kích cỡ chip, Chiang Shang-yi, khi đó là giám đốc nghiên cứu và phát triển của TSMC, nghĩ rằng ông đã có giải pháp. Thay vì ép nhiều bóng bán dẫn vào khối chip vốn đã bé, Shang-yi đề xuất với Morris Chang, nhà sáng lập TSMC, rằng công ty nên khám phá việc đóng gói chip – một quy trình vốn kém tiên tiến và ít được chú ý.

“Tôi nói với ông Chang rằng quá trình phát triển chip tuân theo Định luật Moore có thể chậm lại những năm tới, do đó chúng ta nên thử một thứ gì đó khác để cải thiện hiệu suất”, ông Shang-yi kể.

Một công nhân trong phòng sạch của nhà máy Intel ở Indonesia. Ảnh: Intel

Định luật Moore do Gordon Moore, nhà đồng sáng lập Intel, đưa ra năm 1965, trong đó nói số bóng bán dẫn (transistor) trên mạch tích hợp sẽ tăng gấp đôi mỗi năm, sau đó được sửa đổi thành chu kỳ 18 tháng. Phát hiện này cũng trở thành nền móng cho một dự báo khác: nhân đôi số bóng bán dẫn đồng nghĩa tăng gấp đôi hiệu suất của CPU theo chu kỳ tương tự.

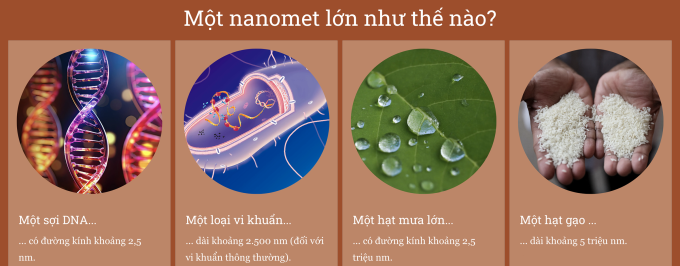

Trước đó, bóng bán dẫn có kích thước khoảng một centimet. Sau cột mốc trên, chúng được đo bằng milimet. Ngày nay, chúng đã thu về mức nanomet (nm) và chỉ tương đương đường kính DNA của con người.

Định luật Moore định hình sự phát triển của ngành công nghiệp chip trong nhiều thập kỷ. Những bước tiến trong quá trình thu nhỏ chip thúc đẩy toàn bộ ngành công nghiệp từ PC, điện thoại thông minh cho đến làn sóng gần nhất là chip xử lý cho AI. Cuộc đua cũng khiến các công ty như TSMC của Đài Loan, Intel của Mỹ hay Samsung của Hàn Quốc chi hàng tỷ USD mỗi năm để làm ra những mẫu chip với kích thước bóng bán dẫn nhỏ hơn nữa, đẩy Định luật Moore đến giới hạn.

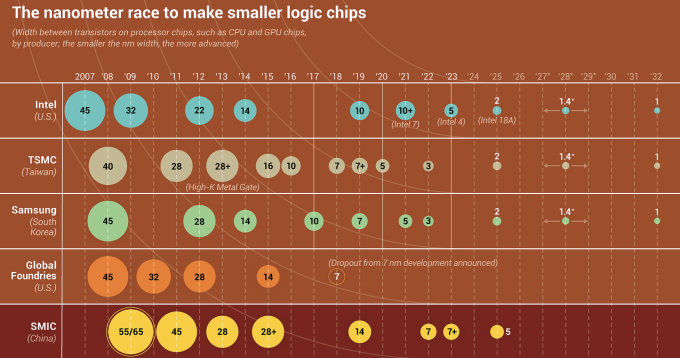

Khả năng thu nhỏ bóng bán dẫn với kích thước nanomet giai đoạn 2007-2013 và dự đoán đến 2032. Nguồn: Nikkei Asia Reseach

“Nếu Định luật Moore thực sự đạt đến giới hạn, nó sẽ gây ảnh hưởng rất lớn cho ngành bán dẫn”, Shang-yi nói. “Nếu không có giải pháp, 20 năm nữa, lĩnh vực chip có nguy cơ trở thành ngành công nghiệp truyền thống, thay vì ngành công nghệ cao như hiện nay”.

Trò chơi đuổi bắt

Có những dấu hiệu cho thấy nhận xét của Shang-yi đang trở thành sự thật. Một trong những bằng chứng lớn nhất là khoảng cách giữa công ty dẫn đầu với công ty đuổi theo phía sau ngày càng thu hẹp.

“Chạy nhanh hơn người chạy nhanh nhất rất khó. Nhưng đến khi người nhanh nhất không thể chạy nhanh hơn nữa, người phía sau sẽ bắt kịp”, Dan Hutcheson, Phó chủ tịch công ty nghiên cứu TechInsights, cho biết. “Trong một cuộc đua chip, người dẫn đầu không được phép vấp ngã, dù chỉ một lần”.

Theo phân tích của Nikkei Asia, khoảng cách công nghệ giữa Intel và SMIC của Trung Quốc đang thu hẹp. Intel hiện sản xuất chip 5 nm, còn SMIC đã có chip 7 nm. Giới chuyên gia đánh giá một phần nguyên nhân do quyết tâm tự chủ bán dẫn của Trung Quốc, nhưng đó cũng là hệ quả của sự chậm lại đối với các đầu tàu. Intel từng đi trước đối thủ Trung Quốc ít nhất 4 hoặc 5 năm, tương đương hơn hai thế hệ về mặt sản xuất chip. Bây giờ, khoảng cách là ba năm, hay 1,5 thế hệ.

TSMC và Samsung hiện đã sản xuất chip 3 nm, trong khi Intel đang là 5 nm. Cả ba đang chạy đua sản xuất chip 2 nm năm 2025. Đến 2032, ba hãng này dự kiến sản xuất được chip 1 nm.

So sánh một nanomet với các vật thể. Nguồn: Nikkei Asia

Nanomet về mặt kỹ thuật đề cập đến chiều rộng của cổng trên bóng bán dẫn. Cổng càng nhỏ càng cho phép ép nhiều bóng bán dẫn hơn vào cùng một khu vực, giúp bộ xử lý mạnh hơn. Nhưng độ nhỏ sẽ đi tới giới hạn, tức việc thu nhỏ cổng hơn nữa là điều không thể. Vì thế, các công ty phải nghĩ ra cách làm mới.

Trước đây, hầu hết công ty sản xuất bán dẫn sử dụng cấu trúc hai chiều. Intel là hãng đầu tiên chuyển bóng bán dẫn của mình sang cấu trúc 3D, tên là FinFET, năm 2012. TSMC và Samsung nhanh chóng làm theo.

Giờ đây, những gã khổng lồ về chip đang nhắm tới một cấu trúc bóng bán dẫn thậm chí phức tạp hơn, gọi là Gate-all-around để tăng sức mạnh cho chip. Cấu trúc mới đắt đỏ, nhưng các hãng buộc phải chạy theo.

Tổng chi tiêu vốn của TSMC, Intel và Samsung Electronics năm 2022 là hơn 97 tỷ USD, cao gấp đôi số tiền mà EU dự định dùng để phát triển lĩnh vực chip một thập kỷ tới. “Chi phí đang làm cho mọi thứ chậm lại. Trước đây, TSMC áp dụng công nghệ mới hai năm một lần, hiện là ba năm và tương lai có thể lâu hơn”, Handel Jones, một chuyên gia kỳ cựu về bán dẫn và CEO của công ty tư vấn chip International Business Strategies, cho biết.

Tốc độ Định luật Moore chậm lại đã mang đến cho các công ty như SMIC cơ hội “nghìn năm có một” trong việc thu hẹp khoảng cách với các công ty dẫn đầu toàn cầu. “Cơ hội tốt đang đến với các doanh nghiệp Trung Quốc”, chuyên gia Wu Hanming thuộc Học viện Kỹ thuật Trung Quốc, nhận xét.

Đóng gói chip – chiến trường mới

TSMC bắt đầu khám phá giải pháp thay thế cho việc thu nhỏ chip thông qua đóng gói một cách nghiêm túc từ 2009. Đóng gói chip ban đầu đơn thuần được xem là cách để bảo vệ mạch tích hợp. Nó không có quá nhiều yêu cầu về công nghệ khi so với việc chế tạo chip và cũng không đem lại sự cải thiện về hiệu suất như việc tăng số lượng bóng bán dẫn.

Tuy nhiên, Shang-yi nhận ra việc kết nối các chip khác nhau, chẳng hạn bộ nhớ và bộ xử lý, theo những cách mới có thể mang lại cải tiến to lớn. Ông đã thuyết phục nhà sáng lập Chang cấp ngân sách 100 triệu USD cùng đội ngũ 400 người để hiện thực hóa ý tưởng.

Thành công không đến lập tức. “Một số giám đốc TSMC thậm chí cười nhạo, nói đề xuất của tôi đã biến TSMC thành một doanh nghiệp chỉ chạy 50 tấm wafer mỗi tháng”, Shang-yi kể.

Nhưng hiện tại, đóng gói chip trở thành chiến trường mới. Năm nay, lần đầu tiên sau 40 năm, Intel phải thiết kế lại kiến trúc chip của mình nhằm tận dụng ưu thế khi đóng gói chip.

Cỗ máy sản xuất chip bên trong nhà máy TSMC. Ảnh: TSMC

H100 của Nvidia, GPU đứng sau sức mạnh của ChatGPT, là hình ảnh thu nhỏ của xu hướng mới. Thiết kế tích hợp của nó kết nối trực tiếp bộ xử lý đồ họa với sáu chip nhớ băng thông cao bằng công nghệ đóng gói tiên tiến do TSMC thực hiện.

Năm 2021, Intel và TSMC bắt tay vào kế hoạch mở rộng đóng gói chip có quy mô lớn nhất với hàng chục tỷ USD. Ngay cả chính phủ Mỹ cũng bắt đầu chú ý đến lĩnh vực này khi dành ba tỷ USD cho nghiên cứu đóng gói chip, bên cạnh khoản trợ cấp bán dẫn 52 tỷ USD.

“Chúng ta đang trong cuộc đua xếp tất cả chip theo mô hình ba chiều, giống một chiếc bánh kếp, sau đó đóng thành gói duy nhất”, Lars Reger, CTO của NXP Semiconductors, nhận xét.

Cơ hội cho Trung Quốc

“Bạn không cần có quá nhiều thiết bị hiện đại, phức tạp để đóng gói chip, cũng như có thể sử dụng công nghệ đóng gói để đẩy tiến trình từ 7 nm lên 5 nm và thậm chí là 3 nm”, một giám đốc của Kinsus Interconnect Technology, một nhà cung cấp chất nền chip cho Nvidia và AMD, nói. “Vì vậy, theo cách nào đó, sự chậm lại của Định luật Moore là điểm tốt để nhà sản xuất chip Trung Quốc thu hẹp khoảng cách với những cái tên dẫn đầu”.

David Ma, Chủ tịch công ty chuyên xây dựng hệ thống hỗ trợ sản xuất bán dẫn Nova Technology, cho rằng lĩnh vực đóng gói chip đang phát triển sẽ “mang đến cho Trung Quốc một cơ hội đi tắt”.

Các công ty Trung Quốc như SMIC hay Huawei đang thực hiện đợt mở rộng lớn nhất từ trước đến nay, khi đã đầu tư 24 tỷ USD vào chi tiêu vốn từ năm 2020 đến 2023. Dù khả năng còn hạn chế, SMIC vẫn cam kết sẽ đạt mục tiêu sản xuất chip 5 nm và thậm chí 3 nm với đội ngũ R&D chuyên trách do đồng CEO Liang Mong-Song, một chuyên gia kỳ cựu của TSMC và Samsung, dẫn đầu.

Trong khi đó, Huawei đã chi gần 81 tỷ USD cho R&D giai đoạn từ 2019 – khi bị Mỹ đưa vào danh sách thực thể – đến nay. Thực tế, đơn vị HiSilicon của Huawei đã thiết kế thành công chip 5 nm và đặt hàng TSMC sản xuất trước khi bị cấm.

“Huawei có thành tích đã được chứng minh về thiết kế chip tiên tiến không kém của Apple và Nvidia. Công ty là quân bài chủ chốt đằng sau sự tiến bộ về chip của Trung Quốc”, Brady Wang, nhà phân tích công nghệ của hãng nghiên cứu Counterpoint Research, nhận xét.

Các công ty nhỏ hơn về chip đang mọc lên tại Trung Quốc. Tại tỉnh Giang Tô, SJ Semiconductor, công ty đóng gói chip mới nổi được nhà nước hậu thuẫn, đang nghiên cứu công nghệ tương tự TSMC. Một công ty lắp ráp chip hàng đầu khác là Quliang Electronics ở thành phố Tuyền Châu dự kiến mở rộng công suất ít nhất gấp bốn lần trong ba năm tới.

“Trung Quốc đang tăng tốc về khả năng đóng gói chip”, một CEO chuỗi cung ứng chip tiết lộ. “Họ đang theo dõi các động thái trong ngành, dù chưa có công nghệ đóng gói hoàn chỉnh để sử dụng đại trà”.