Kioxia và WD trình bày chi tiết về 3D NAND với hơn 300 lớp

Kioxia và đối tác nghiên cứu và sản xuất Western Digital có kế hoạch tiết lộ những cải tiến của họ sẽ cho phép các thiết bị bộ nhớ 3D NAND có dung lượng cao hơn và hiệu suất cao hơn tại Hội nghị chuyên đề về Công nghệ và Mạch VLSI năm 2023 sắp tới. Các kỹ sư của hai công ty đang tìm cách kích hoạt các thiết bị NAND 3D 8 mặt phẳng cũng như IC 3D NAND với hơn 300 dòng từ, theo báo cáo của eeNewsEurope.

NAND 3D tám mặt phẳng: Tối đa 205 MB/s

Khi các thiết bị 3D NAND tăng số lượng dòng từ, thu nhỏ kích thước của các ô NAND và khuếch đại dung lượng của IC bộ nhớ, điều quan trọng là phải tăng hiệu suất đọc/ghi của chúng. Các thiết bị thực tế như ổ SSD, máy tính xách tay và điện thoại thông minh tốt nhất có xu hướng sử dụng ít chip hơn cho một dung lượng nhất định, nhưng người dùng cuối mong muốn thiết bị mới của họ nhanh hơn thiết bị cũ.

Một trong những cách để cải thiện hiệu suất của IC 3D NAND là tăng số lượng mặt phẳng và tăng cường tính song song bên trong của nó. Kioxia sẽ trình bày một bài báo (C2-1) về thiết bị 1Tb 3D TLC NAND tám mặt phẳng với hơn 210 lớp hoạt động và giao diện 3,2 GT/s. IC này gần giống với thiết bị NAND TLC 1Tb 3D 218 lớp của Kioxia/Western Digital với mật độ 17Gb/mm^2 và bus I/O 3,2 GT/s được giới thiệu vào cuối tháng 3, nhưng thiết bị này có tám mặt phẳng thay vì bốn và là được cho là cung cấp thông lượng chương trình 205 MB/giây cũng như độ trễ đọc là 40 μs. Thông số sau này tốt hơn đáng kể so với 56 μs do NAND 3D 128 lớp của Kioxia cung cấp.

Bài báo mới tiết lộ rằng thiết bị 1Tb 3D TLC NAND của Kioxia đã đạt được tốc độ giao diện 3,2 GT/s bằng cách giảm vùng truy vấn dữ liệu theo hướng X xuống 41%, cho phép truyền dữ liệu nhanh hơn giữa bộ nhớ và máy chủ. Tuy nhiên, thiết kế mới này có thể dẫn đến tắc nghẽn dây dẫn, điều mà Kioxia đã giảm thiểu bằng cách giới thiệu bộ giải mã địa chỉ hàng lai (X-DEC). X-DEC giúp quản lý mật độ dây gia tăng một cách hiệu quả, giảm thiểu sự suy giảm độ trễ đọc có thể xảy ra do tắc nghẽn.

Kioxia cũng triển khai kỹ thuật một xung hai nhấp nháy cho phép hai ô nhớ được cảm nhận trong một xung duy nhất, giảm 18% thời gian cảm nhận tổng thể và tăng thông lượng chương trình lên 205 MB/s. Kiến trúc tám mặt phẳng mới lạ của thiết bị, phương pháp một xung hai nhấp nháy và tốc độ I/O 3,2 GT/s cho phép độ trễ đọc là 40 μs và thông lượng chương trình là 205 MB/s.

Có vẻ như thiết bị 1Tb 3D TLC NAND đã triển khai bộ giải mã địa chỉ hàng lai và kỹ thuật một xung hai nét cho giao diện tốc độ của nó và những công nghệ này có thể sẽ được sử dụng rộng rãi trong tương lai. Tuy nhiên, việc triển khai kiến trúc tám mặt phẳng làm tăng độ phức tạp của cả IC 3D NAND và bộ điều khiển bộ nhớ hỗ trợ, dẫn đến chi phí sản xuất và phát triển cao hơn cũng như thời gian đưa sản phẩm ra thị trường lâu hơn. Ngoài ra, nếu bộ điều khiển máy chủ không thể quản lý thiết bị tám mặt phẳng đúng cách, thì hiệu suất thực tế của IC có thể giảm.

> NAND 3D 300 lớp

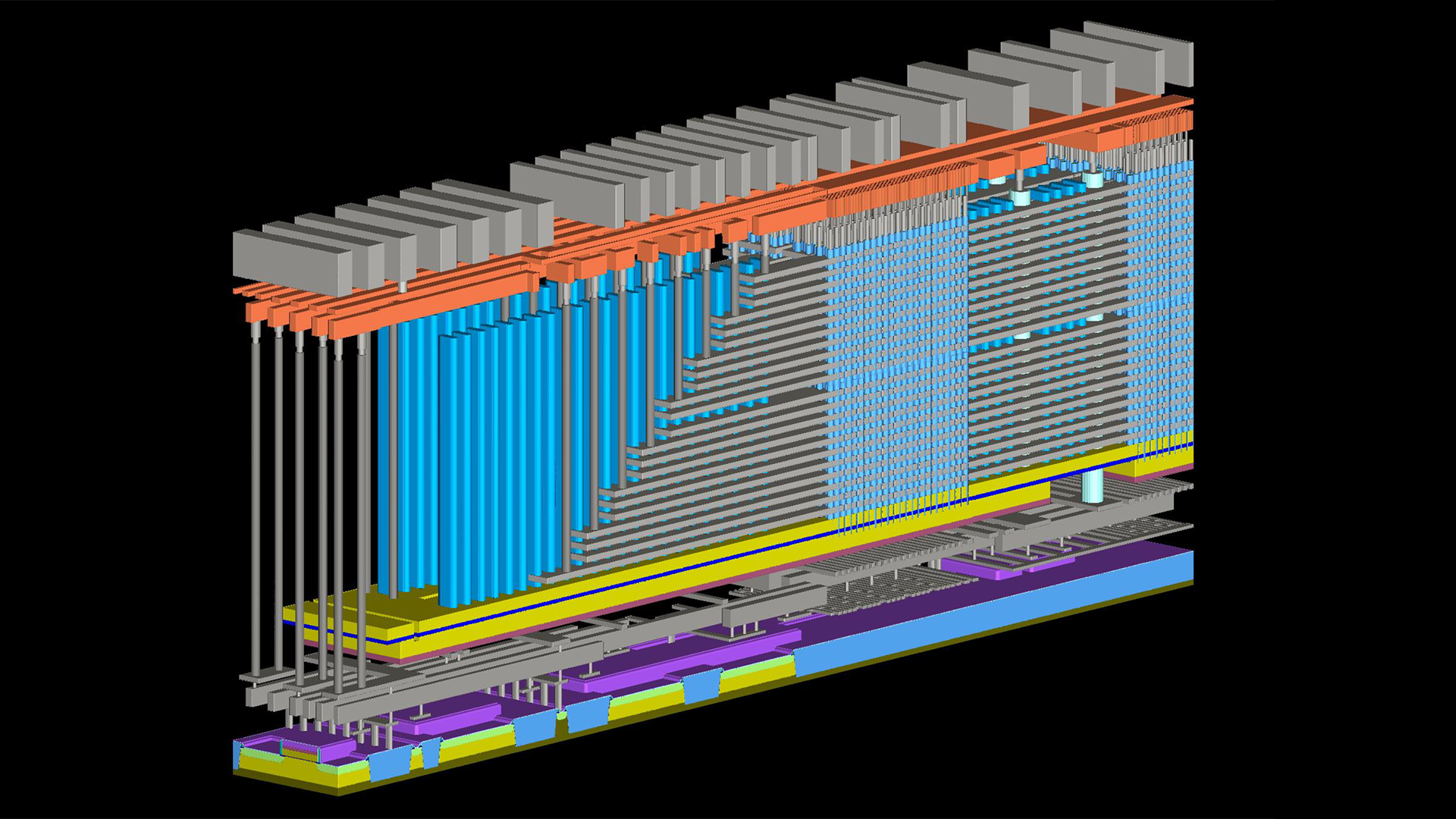

Bên cạnh việc nghiên cứu cấu trúc thiết bị IC 3D NAND tám mặt phẳng, Kioxia và Western Digital cũng đang hợp tác để phát triển các thiết bị 3D NAND với hơn 300 lớp từ hoạt động, giúp tăng cường độ dài kênh dọc và nâng cao chất lượng kết tinh của kênh.

Để đạt được điều này, các công ty có kế hoạch sử dụng các kỹ thuật Kết tinh bên cảm ứng kim loại (MILC), như đã nêu trong bài báo T7-1. Bằng cách sử dụng MILC, các nhà phát triển có thể tạo ra các kênh silicon (Si) ‘giống mì ống’ dài 14 micron kết tinh đơn bên trong các lỗ bộ nhớ dọc, mặc dù đối với thiết bị nguyên mẫu 112 lớp.

IC 3D NAND thử nghiệm này cũng được báo cáo là tận dụng phương pháp thu niken tiên tiến để loại bỏ tạp chất và khuyết tật khỏi vật liệu silicon, do đó nâng cao hiệu suất của mảng tế bào. Kết quả là, tiếng ồn đọc được giảm tối thiểu 40% và độ dẫn của kênh được tăng lên gấp 10 lần mà không làm giảm độ tin cậy của tế bào.

>NAND 3D 400 lớp

Hiện tại, các kỹ thuật như xếp chồng chuỗi cho phép xây dựng 3D NAND với hàng trăm lớp hoạt động, nhưng chúng tốn nhiều thời gian. Do đó, các nhà sản xuất thiết bị và nhà sản xuất thiết bị wafer fab đang phát triển các phương pháp để tăng số lượng lớp bằng cách khắc các kênh dọc dài hơn (sâu hơn).

Tokyo Electron, một nhà sản xuất công cụ khắc, chuẩn bị trình bày một bài báo (T3-2) mô tả chi tiết phương pháp khoan nhanh các kênh dọc hơn 10 micron (10 μm) cho các nút NAND 3D 400 lớp mà không tiêu thụ hoặc sử dụng năng lượng quá mức. của các chất độc hại.

Theo Tokyo Electron, công nghệ khắc điện môi Tỷ lệ khung hình cao (HAR) của họ sử dụng giai đoạn wafer đông lạnh và hóa chất khí mới để tạo ra các kênh cao 10 micron với cấu hình khắc “xuất sắc” chỉ trong 33 phút và với tỷ lệ 84%. giảm lượng khí thải carbon.