Intel Chi tiết Công nghệ phân phối điện mặt sau PowerVia

Vào thứ Hai, Intel đã trình bày chi tiết việc triển khai mạng phân phối điện mặt sau (BS PDN) sẽ là một phần của quy trình chế tạo Intel 18A và 20A (18/20 angstroms, lớp 1.8/2.0nm). Ngoài ra, công ty cũng tiết lộ thêm thông tin về những lợi ích mà công nghệ này mang lại cho nút Intel 4 + PowerVia nội bộ được thiết kế dành riêng cho BS PDN tốt nhất.

Cung cấp năng lượng mặt sau

Các công nghệ sản xuất 18A và 20A của Intel sẽ giới thiệu hai cải tiến quan trọng: bóng bán dẫn hiệu ứng trường toàn cổng RibbonFET (GAAFET) và mạng phân phối điện mặt sau PowerVia. Những ưu điểm của bóng bán dẫn GAA đã được thảo luận trước đây và nằm ngoài phạm vi của thông báo ngày hôm nay. Thay vào đó, chúng tôi sẽ tập trung vào việc cung cấp năng lượng ở mặt sau.

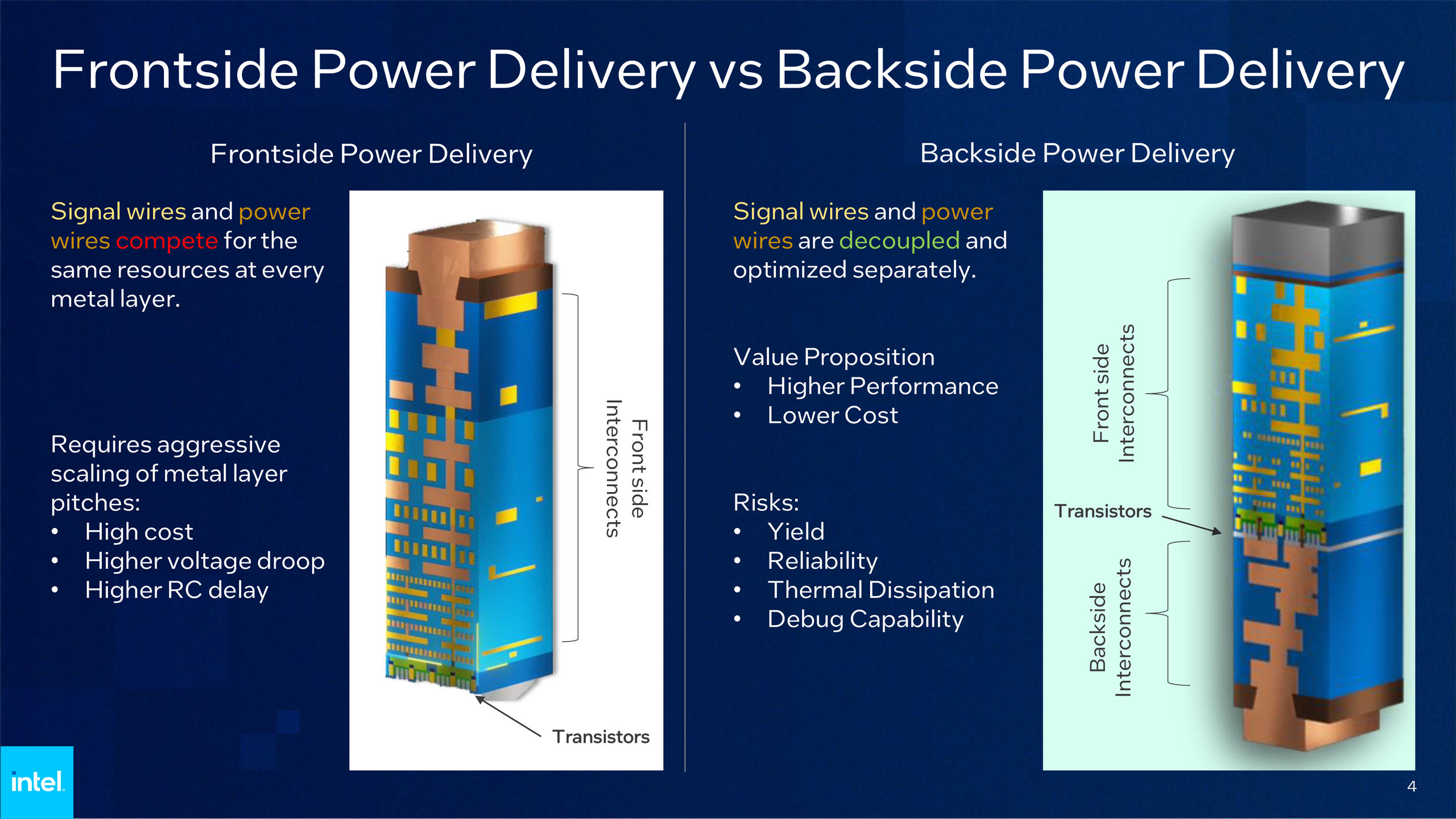

Đường ray điện phía sau nhằm mục đích tách biệt hệ thống dây điện và I/O, chuyển các đường dây điện ra phía sau tấm wafer. Phương pháp này giải quyết các vấn đề như tăng thông qua điện trở ở cuối dòng (BEOL), cuối cùng là cải thiện hiệu suất của bóng bán dẫn và giảm mức tiêu thụ điện năng của chúng. Nó cũng loại bỏ mọi nhiễu có thể xảy ra giữa dữ liệu và dây nguồn, đồng thời tăng mật độ bóng bán dẫn logic.

Theo thời gian, BD PDN sẽ trở thành một tính năng tiêu chuẩn của chip, nhưng hiện tại Intel coi đây là một cải tiến mang tính đột phá lớn giống như silicon căng ở 90nm vào năm 2003, cổng kim loại high-K dựa trên Hafnium ở 45nm vào năm 2007 và FinFET ở 22nm vào năm 2012 .

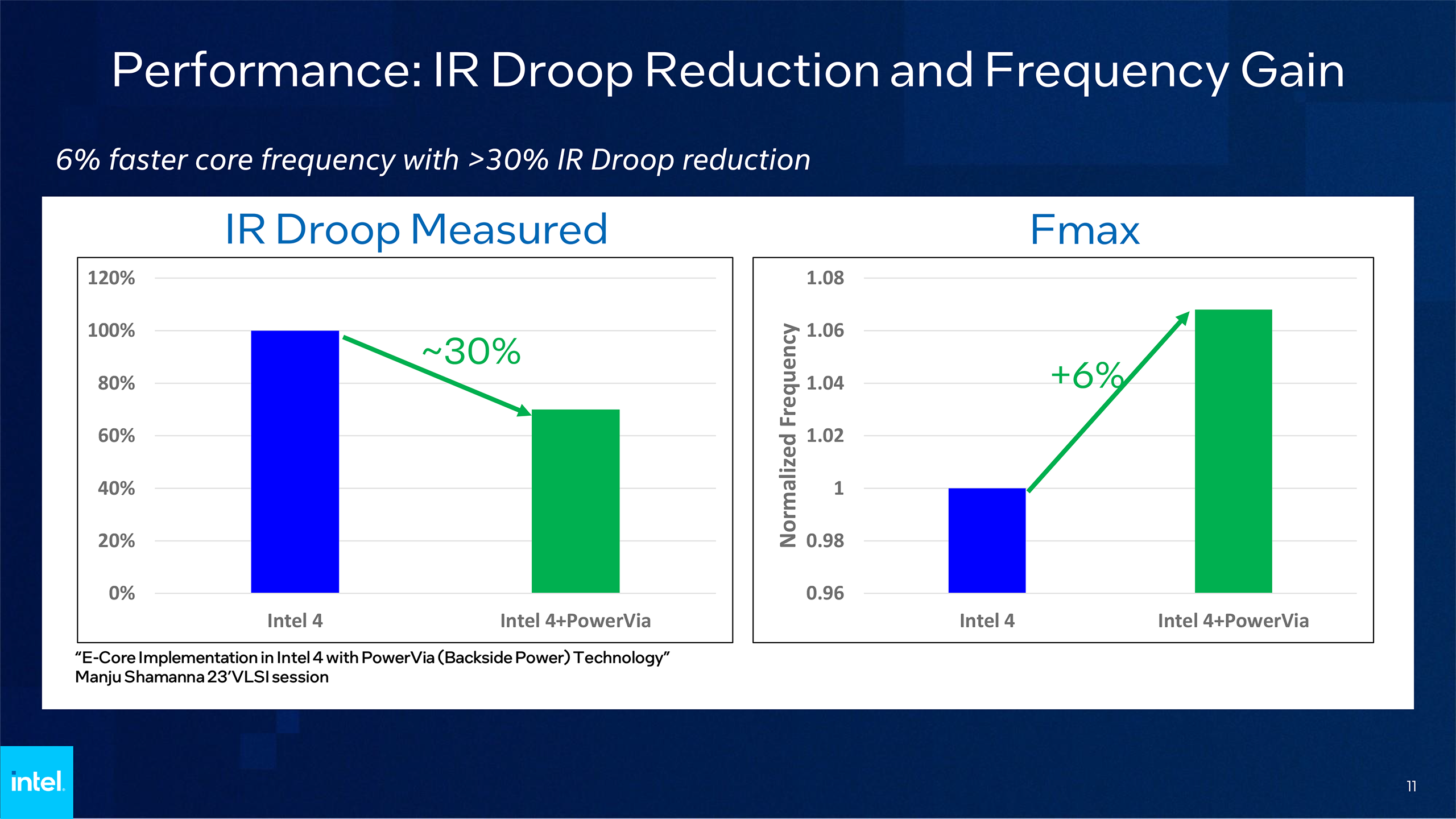

Intel cho biết khi được triển khai trong một chip thử nghiệm trên một nút xử lý nội bộ, PDN mặt sau của nó đã cho phép nó tăng tốc độ xung nhịp lên hơn 6%, giảm 30% điện áp IR sụt giảm và tăng mức sử dụng tế bào trên các khu vực rộng lớn của khuôn E-core. đến hơn 90%. Mặc dù có những lợi ích, nhưng việc triển khai và xây dựng hệ thống cung cấp năng lượng từ phía sau là một thách thức vì nhiều lý do.

Xây dựng PowerQua Backside PDN

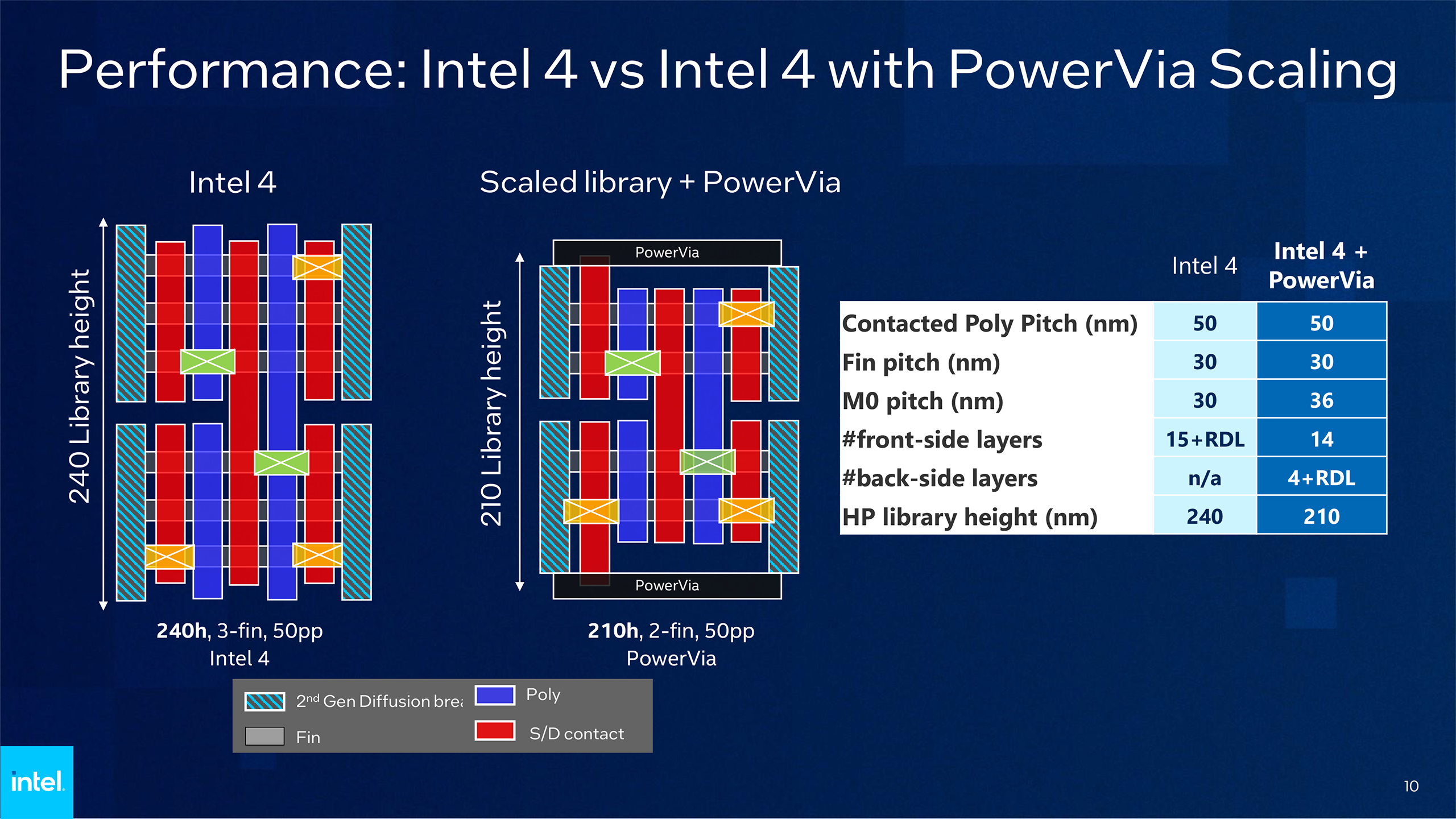

Xây dựng PDN mặt sau rất khác so với việc cung cấp năng lượng mặt trước truyền thống. Ngày nay, việc sản xuất ngay cả những con chip tiên tiến nhất cũng khá đơn giản. Quá trình chế tạo mọi tấm wafer bắt đầu từ lớp bóng bán dẫn M0 phức tạp nhất với bước sóng nhỏ tới 30nm (đối với nút Intel 4) bằng cách sử dụng các công cụ sản xuất tinh vi nhất như máy quét EUV. Sau đó, các nhà sản xuất chip xây dựng các lớp bóng bán dẫn ít phức tạp hơn trên lớp đầu tiên, tăng dần kích thước khi họ cần kết nối tất cả các lớp và cấp nguồn cho tất cả các bóng bán dẫn.

Các dây vật lý thực tế cho I/O và nguồn trông có vẻ khổng lồ khi so sánh với các lớp bóng bán dẫn và việc định tuyến chúng đúng cách với mọi thế hệ mới sẽ trở nên khó khăn và tốn kém hơn.

Xử lý một tấm wafer với các chip có PowerVia BS PDN của Intel liên quan đến việc tạo ra tất cả các lớp logic phức tạp cũng như dây tín hiệu, sau đó lật tấm wafer và xây dựng mạng phân phối điện ‘trên cùng’ logic. Trên lý thuyết, một cú ‘lật kèo’ như vậy có vẻ không phải là vấn đề lớn. Tuy nhiên, nó bổ sung khá nhiều bước quy trình, bao gồm loại bỏ silicon ‘dư thừa’ khỏi wafer để xây dựng PDN trên các bóng bán dẫn logic, làm sạch CMP, đo lường, in thạch bản và khắc, v.v.

Một vòng lặp quy trình như vậy có thể không yêu cầu các công cụ tiên tiến nhất trong fab, nhưng nó vẫn tốn tiền. Thật vậy, một slide của Intel chỉ ra rằng công nghệ xử lý Intel 4 sử dụng 15 lớp kim loại và lớp phân phối lại (RDL), trong khi Intel 4 + PowerVia sử dụng 14 lớp mặt trước, 4 lớp mặt sau và RDL, giúp tăng tổng số lớp đến 18 + RDL.

Ben Sell, phó chủ tịch phát triển công nghệ của Intel cho biết: “Các bóng bán dẫn được chế tạo trước, như trước đây, với các lớp kết nối được thêm vào tiếp theo. “Bây giờ là phần thú vị: lật tấm wafer và đánh bóng mọi thứ để lộ lớp dưới cùng mà dây dẫn […] cho sức mạnh sẽ được kết nối. Chúng tôi gọi nó là công nghệ silicon, nhưng lượng silicon còn lại trên những tấm wafer này thực sự rất nhỏ.”

Có một số yếu tố cần xem xét với PDN mặt sau. Đầu tiên, nó thay đổi mạnh mẽ quy trình sản xuất, vì vậy Intel phải tìm cách đảm bảo năng suất cao bất chấp những thay đổi triệt để. Thứ hai, Intel phải đảm bảo rằng PDN mặt sau cũng đáng tin cậy như PDN hiện tại và hoạt động như dự định. Thứ ba, vì I/O và dây nguồn hiện được đặt trên cả hai mặt của bóng bán dẫn, nên việc làm mát chip trong tương lai sẽ khó khăn hơn. Thứ tư, việc gỡ lỗi chip trở nên khó khăn hơn nhiều vì giờ đây Intel phải loại bỏ các kết nối nguồn phía sau để truy cập các lớp bóng bán dẫn.

Có một điểm đặc biệt khác về quy trình PowerVia của Intel. Bởi vì Intel loại bỏ silicon dư thừa khỏi mặt sau của tấm wafer nên họ tin rằng nó sẽ mất độ cứng, đó là lý do tại sao họ liên kết một tấm wafer sóng mang ở phía tín hiệu của tấm wafer để giữ cấu trúc lại với nhau. Tấm wafer sóng mang đó cuối cùng cũng được làm mỏng đi, nhưng việc bổ sung nó cũng là một bước quy trình phức tạp (và có lẽ là cần thiết).

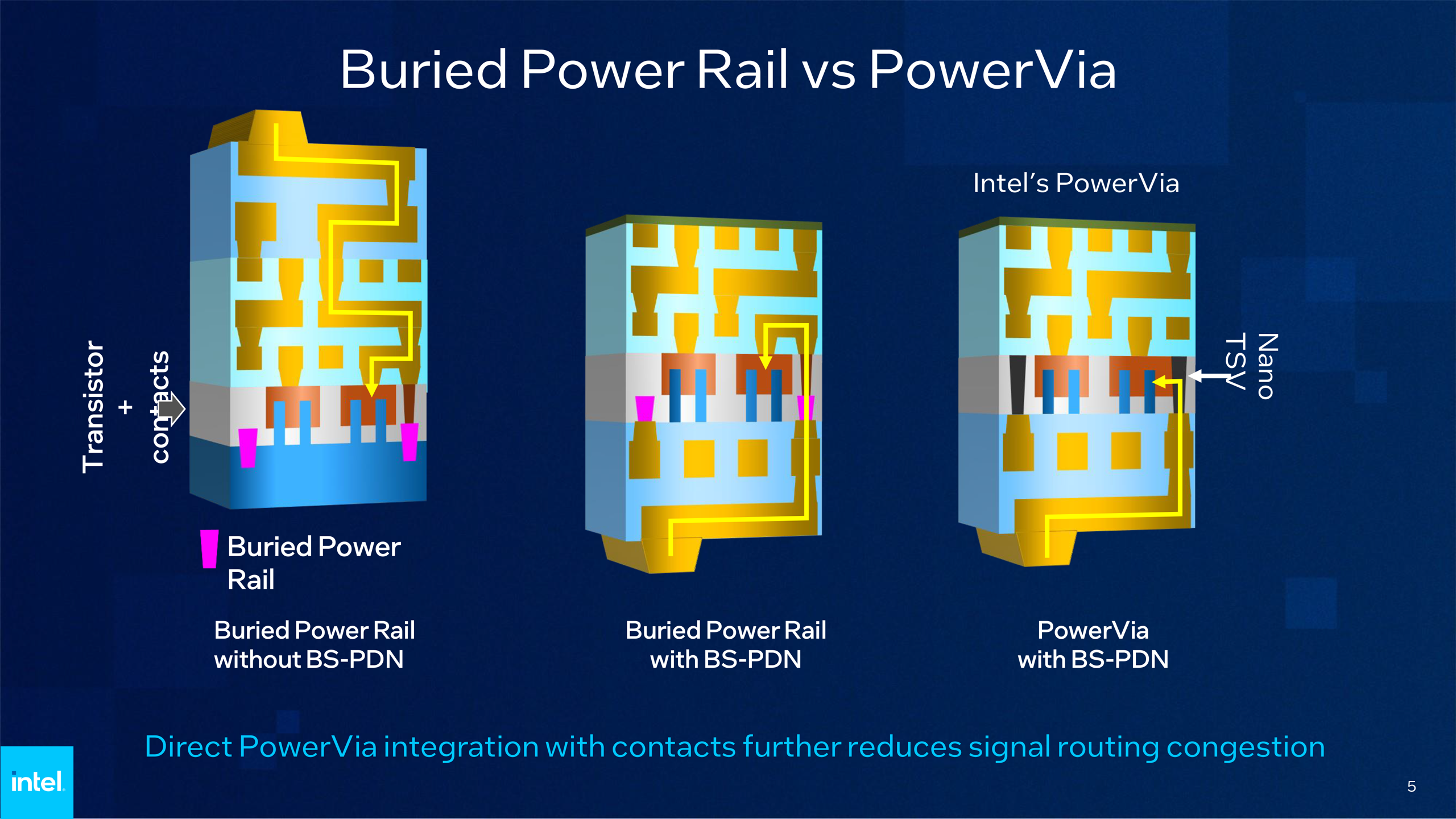

Một điều khác về PDN mặt sau PowerVia của Intel là nó không sử dụng đường ray nguồn chôn với BS PDN, mà thay vào đó sẽ dựa vào kích thước nano thông qua silicon vias (TSV) để cung cấp điện ngay cho lớp bóng bán dẫn. Đây rõ ràng là lý do tại sao công ty gọi công nghệ của mình là PowerVia.

Kiểm tra mạng phân phối điện mặt sau

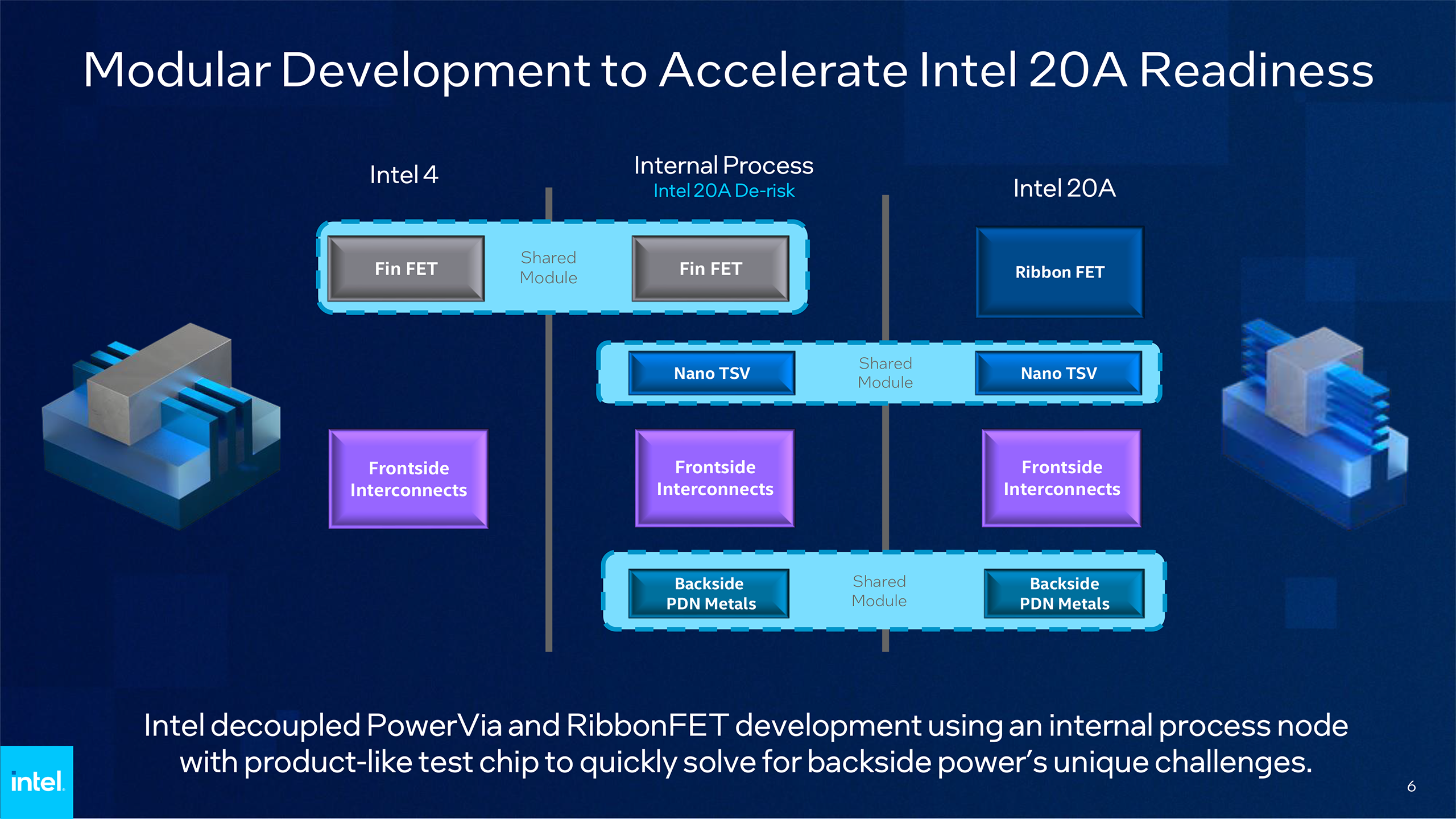

Giờ đây, Intel không còn là người dẫn đầu không thể chối cãi của thị trường chip với các công nghệ xử lý tốt nhất, công ty không thể mạo hiểm với điểm hỏng hóc tiềm ẩn ở một trong các nút thế hệ tiếp theo của mình. Vì vậy, nó đã tách rời quá trình phát triển các bóng bán dẫn RibbonFET GAA và PowerVia BS PDN để làm cho quá trình phát triển dễ dàng hơn một chút bằng cách làm việc trên RibbonFET với PDN thông thường và sau đó gỡ lỗi PowerVia với các FinFET đã được chứng minh.

Để kiểm tra mạng phân phối điện mặt sau PowerVia của mình, Intel đã xây dựng một quy trình sản xuất đặc biệt dựa trên nút Intel 4 sử dụng các bóng bán dẫn FinFET đã được chứng minh, nhưng nó đi kèm với một đường ray điện phía sau thay vì một đường ray điện truyền thống. Quá trình này đương nhiên được gọi là Intel 4 + PowerVia và nó được sử dụng cho một con chip thử nghiệm có tên mã là Blue Sky Creek.

Chip thử nghiệm Blue Sky Creek của Intel sử dụng hai khuôn, mỗi khuôn có bốn lõi tiết kiệm năng lượng dựa trên vi kiến trúc Crestmont. Chúng được thiết kế để hoạt động ở tần số 3 GHz ở 1,1 Volts. Phương tiện thử nghiệm được thiết kế chỉ cho hai mục đích: khám phá những ưu điểm của PowerVia BS PDN và loại bỏ rủi ro từ các công nghệ xử lý 20A/18A trong tương lai bằng cách thử nghiệm tất cả những thứ liên quan đến mạng lưới cung cấp điện mới, bao gồm sản lượng, độ tin cậy của PDN và chip, làm mát và gỡ lỗi.

Khi nói đến hiệu suất, Intel cho biết mật độ lỗi của chip thử nghiệm được triển khai trên Intel 4 và Intel 4 + PowerVia là gần như nhau. Các mục tiêu về độ tin cậy và đặc điểm của bóng bán dẫn cũng đáp ứng được kỳ vọng cần thiết cho quá trình sản xuất. Hơn nữa, nhiệt độ của chiếc xe thử nghiệm phù hợp với mong đợi. Trong khi đó, Intel thừa nhận rằng việc làm mát sẽ là một thách thức với PDN mặt sau, vì vậy hãng đã phát triển các kế hoạch giảm thiểu nhiệt mới để làm mát các chip thế hệ tiếp theo.

Sell giải thích: “Thông thường, bạn cũng sử dụng mặt silicon để tản nhiệt. “Vì vậy, bây giờ bạn đã kẹp các bóng bán dẫn của mình và câu hỏi đặt ra là ‘Chúng ta có vấn đề về nhiệt không? Chúng ta có bị nóng cục bộ không?’ Tại thời điểm này, bạn có thể đoán được câu trả lời: không.”

Gỡ lỗi được cho là một trong những phần phức tạp nhất, nhưng may mắn là các kỹ sư xác thực của Intel đã tìm ra cách khắc phục khó khăn.

Sell cho biết: “Có rất nhiều mối quan tâm và do dự và đó có lẽ là điều khó tìm ra nhất – làm thế nào để gỡ lỗi cho việc cung cấp năng lượng mặt sau mới này”. “Để làm cho mọi thứ trở nên khó khăn hơn, nhóm thiết kế chip thử nghiệm đã cố tình thêm một số lỗi ‘trứng phục sinh’ vào chip mà nhóm xác nhận không hề hay biết. Tin tốt là? Họ đã tìm thấy lỗi. Chúng tôi đã đạt được tiến bộ vượt bậc trong vài năm qua nhiều năm phát triển các khả năng sửa lỗi đó và chứng minh chúng trên Blue Sky Creek.”

PowerVia BS PDN của Intel sẽ ra mắt vào năm 2024

Các công nghệ xử lý có sẵn công khai đầu tiên của Intel để sử dụng mạng phân phối điện mặt sau PowerVia của họ sẽ là các nút 20A và 18A sẽ sẵn sàng đi vào sản xuất lần lượt vào nửa cuối năm 2023 và nửa đầu năm 2024. CPU máy khách đầu tiên của Intel được sản xuất trên quy trình chế tạo 20A là Arrow Lake, dự kiến sẽ ra mắt vào khoảng giữa năm 2024 hoặc sớm hơn.

Các công nghệ sản xuất 18A và 20A của Intel được phát triển cho cả sản phẩm của chính công ty và khách hàng của Intel Foundry Services, vì vậy PowerVia hứa hẹn sẽ mang lại lợi ích cho cả Intel và khách hàng IFS của họ. Việc PowerVia BS PDN có phải là một lợi ích hữu hình hay không thì chỉ có thời gian mới trả lời được, nhưng đáng chú ý là Intel là công ty đầu tiên sẵn sàng sản xuất chip với khả năng cung cấp năng lượng từ mặt sau, vì TSMC dự kiến chỉ cung cấp một công nghệ tương tự trong cuối năm 2026 đến đầu năm 2027.