Chip GAA 3nm đầu tiên của Samsung được tìm thấy trong Cryptominer

Samsung đã chính thức bắt đầu sản xuất số lượng lớn chip trên công nghệ xử lý SF3E (lớp 3nm, cổng đầu vào) của mình khoảng một năm trước, nhưng chưa có nhà thiết kế chip fables nào xác nhận rằng họ sử dụng nút này cho các sản phẩm của mình. Nhưng TechInsights gần đây đã phát hiện rằng công cụ khai thác tiền điện tử Whatsminer M56S++ của MicroBT có một mạch tích hợp dành riêng cho ứng dụng (ASIC) thực sự được tạo ra bằng quy trình SF3E của Samsung.

ASIC được sử dụng để khai thác tiền điện tử có xu hướng là thiết bị nhỏ với số lượng bóng bán dẫn tương đối thấp có cấu trúc logic lặp lại tương tự và số lượng ô bit SRAM tối thiểu. Điều này thường tạo ra những con chip như vậy và Whatsminer M56S++ nói riêng, rất phù hợp để làm chất tẩy rửa đường ống cho các công nghệ sản xuất tiên tiến nhất do tính đơn giản trong sản xuất của chúng. Đối với Samsung Foundry, việc sử dụng SF3E của họ cho các chip như ASIC khai thác tiền điện tử là hoàn toàn hợp lý.

Thật không may, chúng tôi không biết nhiều về Whatsminer M56S++ ASIC ngoại trừ việc máy khai thác của MictoBT dựa trên con chip này có tốc độ băm 240-256 Th/s và hiệu suất năng lượng 22J/T. Đối với những người quan tâm đến việc khám phá thêm về chip, chúng tôi khuyên bạn nên mua một báo cáo thích hợp từ TechInsights.

Thật không may, hiện tại vẫn chưa biết liệu SF3E của Samsung có được sử dụng cho các ứng dụng ngoài chip khai thác tiền điện tử hay không. Nhưng một cách chính thức, Samsung nói rằng họ sản xuất các sản phẩm sử dụng nút quy trình mới nhất của mình.

“Chúng tôi đang sản xuất hàng loạt quy trình 3-nano thế hệ thứ nhất với năng suất ổn định và dựa trên kinh nghiệm này, chúng tôi đang phát triển quy trình thế hệ thứ 2 để đảm bảo khả năng sản xuất hàng loạt lớn hơn nữa”, một báo cáo tài chính do Samsung phát hành cho biết.

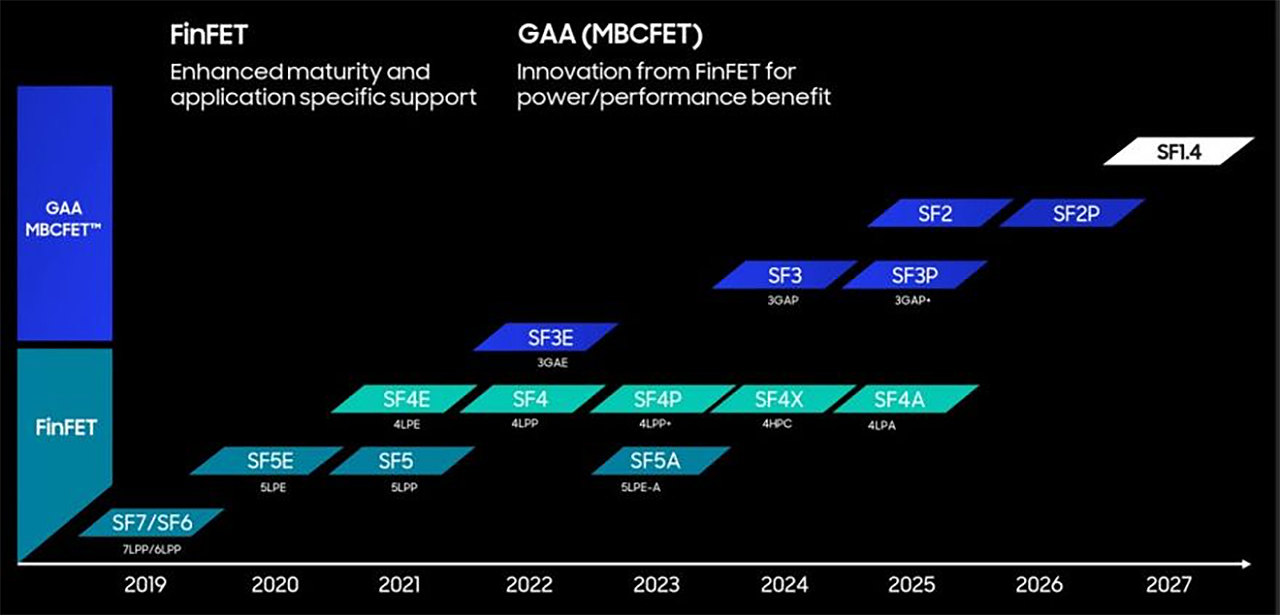

Khi so sánh với công nghệ lớp 5nm thế hệ thứ 2 của Samsung (SF5, 5LPP), SF3E (còn gọi là 3GAE) hứa hẹn sẽ giảm mức tiêu thụ năng lượng của chip tới 45% trong khi vẫn duy trì độ phức tạp và tần số tương tự hoặc có thể nâng cao hiệu suất lên 23% với công nghệ tương tự. số lượng bóng bán dẫn và đồng hồ. Ngoài ra, nó cũng có thể giảm 16% diện tích chiếm dụng của mạch tích hợp (IC). Công ty gần đây đã trình bày chi tiết quy trình lớp 3nm thế hệ thứ hai có tên SF3.