AMD tiết lộ CPU EPYC Bergamo với 128 lõi Zen 4C, hiện có sẵn

AMD đã công bố một loạt sản phẩm mới hôm nay tại sự kiện Ra mắt Trung tâm Dữ liệu và Công nghệ AI ở San Francisco, California. Công ty cuối cùng đã chia sẻ thêm thông tin chi tiết về bộ xử lý EPYC Bergamo 5nm dành cho các ứng dụng gốc trên đám mây và các chip này hiện đang được chuyển đến khách hàng.

AMD cũng đã công bố bộ xử lý Instinct MI300 có các lõi CPU và GPU xếp chồng 3D trên cùng một gói với HBM, cùng với mẫu MI300X chỉ có GPU mới cũng được sử dụng để mang tám bộ tăng tốc lên một nền tảng có dung lượng đáng kinh ngạc 1,5TB. Bộ nhớ HBM3. AMD cũng thông báo rằng bộ vi xử lý EPYC Genoa-X của họ có bộ đệm L3 lên tới 1,1GB. Cả ba sản phẩm này hiện đã có sẵn, nhưng AMD cũng có bộ xử lý EPYC Sienna dành cho công ty viễn thông và sản phẩm tiên tiến sẽ ra mắt vào nửa cuối năm 2023.

AMD EPYC Việt Nam

Bộ xử lý EPYC Bergamo 128 lõi của AMD là CPU gốc x86 đầu tiên trong ngành, được thiết kế cho mật độ lõi cao nhất với lõi Zen 4c được tối ưu hóa giúp giảm một nửa diện tích cần thiết cho mỗi lõi. Các chip này sẽ cạnh tranh với chip Sierra Forest 144 lõi của Intel, đánh dấu sự ra mắt của lõi Hiệu suất (E-core) của Intel trong dòng sản phẩm trung tâm dữ liệu Xeon và bộ xử lý AmpereOne 192 lõi của Ampre, chưa kể đến silicon tùy chỉnh đang được phát triển hoặc được Google và Microsoft tuyển dụng.

Tất cả các dịch vụ này được thiết kế để tối đa hóa hiệu quả sử dụng năng lượng cho các khối lượng công việc có độ trễ cao và song song. Các ví dụ bao gồm triển khai máy ảo mật độ cao, phân tích dữ liệu và dịch vụ web mặt trước. Các chip này cung cấp số lượng lõi cao hơn so với các giải pháp trung tâm dữ liệu tiêu chuẩn, với tần số và đường bao điện năng thấp hơn.

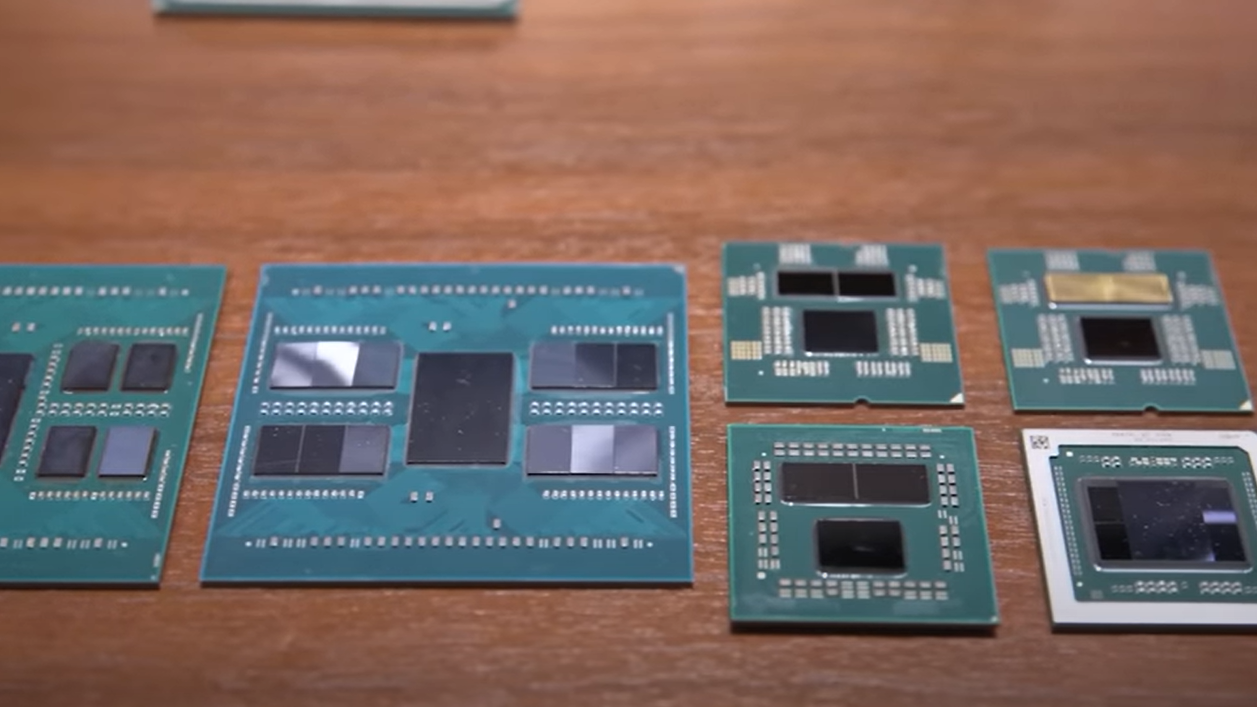

Bergamo của AMD có 128 lõi và rơi vào các nền tảng máy chủ sử dụng cùng một ổ cắm SP5 như bộ xử lý EPYC Genoa 96 lõi tiêu chuẩn. Giống như các đối tác thông thường của họ, Bergamo hỗ trợ bộ nhớ 12 kênh chạy ở DDR5-4800. AMD rèn chip bằng cách kết hợp các chiplet có lõi Zen 4c với khuôn I/O trung tâm ‘Floyd’ hiện có của công ty, do đó liên kết các chiplet tính toán với bộ nhớ và chiplet I/O dựa trên nút quy trình cũ hơn.

| Hàng 0 – Ô 0 | Số lõi / Chủ đề tối đa | Cơ sở/Tăng cường (GHz) | TDP mặc định | Bộ đệm L3 |

| 9754 | 128 / 256 | 2,25 / 3,1 | 360W | 256 MB |

| 9754S | 128 / 128 | 2,25 / 3,1 | 360W | 256 MB |

| 9734 | 112 / 224 | 2.2 / 3.0 | 320W | 256 MB |

Hiện tại, AMD đã công bố hai bộ xử lý Bergamo nói trên, EPYC 9754 với 128 nhân/256 luồng và EPYC 9734 với 112 nhân/224 luồng. Loại thứ hai có hai lõi trên mỗi CCD bị vô hiệu hóa. Hầu hết các thông số kỹ thuật còn lại ngoài số lượng lõi đều giống nhau, vì vậy 9734 vẫn có đầy đủ 16 MB bộ nhớ đệm L3 trên mỗi CCX và tổng bộ nhớ đệm L3 là 256 MB. AMD tuyên bố hiệu suất năng lượng tăng gấp 2,7 lần với chip Bergamo.

AMD đã chia sẻ một vài nét khái quát về kiến trúc Bergamo, bao gồm cả việc nó có vùng đệm lõi + L3 là 2,48mm^2, nhỏ hơn 35% so với 3,84mm^2 mà nó đạt được trên cùng nút tiến trình với Zen tiêu chuẩn 4 nhân. AMD sử dụng tám CCD 16 lõi để đạt được số lượng lõi cao nhất là 128 lõi.

Một điều thú vị cần lưu ý là hiện tại, AMD chỉ sử dụng tám bộ ba Zen 4C với bộ ba IO trung tâm, trong khi các chip EPYC tiêu chuẩn sử dụng tới mười hai bộ ba Zen 4. Liệu chúng ta có thể thấy một giải pháp Zen 4C trong tương lai với 12 chiplet và 192 lõi không? Có lẽ, mặc dù AMD vẫn chưa công bố một thiết kế như vậy nên chúng ta sẽ phải chờ xem.

Hôm nay, chúng tôi đang tìm hiểu thêm các chi tiết kiến trúc chuyên sâu của các con chip, hãy chú ý theo dõi để biết thêm thông tin.