AMD EPYC ‘Siena’ Specification Leak: Up to 64 Cores

Renowned hardware leaker @momomo_us has published what seems to be specifications of AMD’s upcoming EPYC 8004-series ‘Siena’ processors. The new Zen 4-based CPUs are projected to hit the market later this year or early next year and address lower-power servers that may not need the highest performance, such as those used for edge and telecom applications.

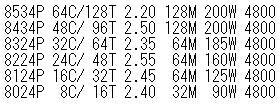

If the specifications published by the leaker is accurate, then AMD’s EPYC 8004-series ‘Siena’ lineup will consist of at least six models featuring eight, 16, 24, 32, 48, and 64 cores operating at 2.20 – 2.55 GHz and consuming from 90W to 200W depending on the model. Meanwhile, AMD’s EPYC ‘Siena’ CPUs will feature an up to 128 MB L3 cache, which is two times smaller than L3 cache of AMD’s EPYC ‘Rome’ processor with 64 cores.

The origin of the specifications is unknown, but leakers like @momomo_us typically obtain their information from documents by chip developers or their partners. While the information may come from a legitimate source, it may be preliminary or outdated, so take it with a grain of salt.

In general, specifications of AMD’s EPYC 8004-series ‘Siena’ processors look rather logical. These CPUs are meant for low power servers with reduced total cost of ownership (TCO) that do not have to be performance champs, but have to be energy efficient and easy to build. Indeed, Siena will top at a 200W TDP, according to the newly published information.

AMD’s Siena is expected to use the company’s new SP6 platform that is considerably less complex than the SP5 platform used for AMD’s EPYC 9000-series processors that are designed to feature the highest core count possible and deliver unbeatable performance for those who need it. For example, SP6 is expected to feature an eight-channel DDR5-4800 memory subsystem that will deliver enough bandwidth for a 64-core CPU, but which is considerably less complex than a 12-channel memory subsystem of AMD’s Genoa, Genoa-X, and Bergamo processors.